II. Rolling Monthly

The present targets for the Total and Cold times are:

Total time per SI Mode per measurement: 7600.0 seconds

Fraction of total time the measurement should be cold: 60.0%

Back To Top

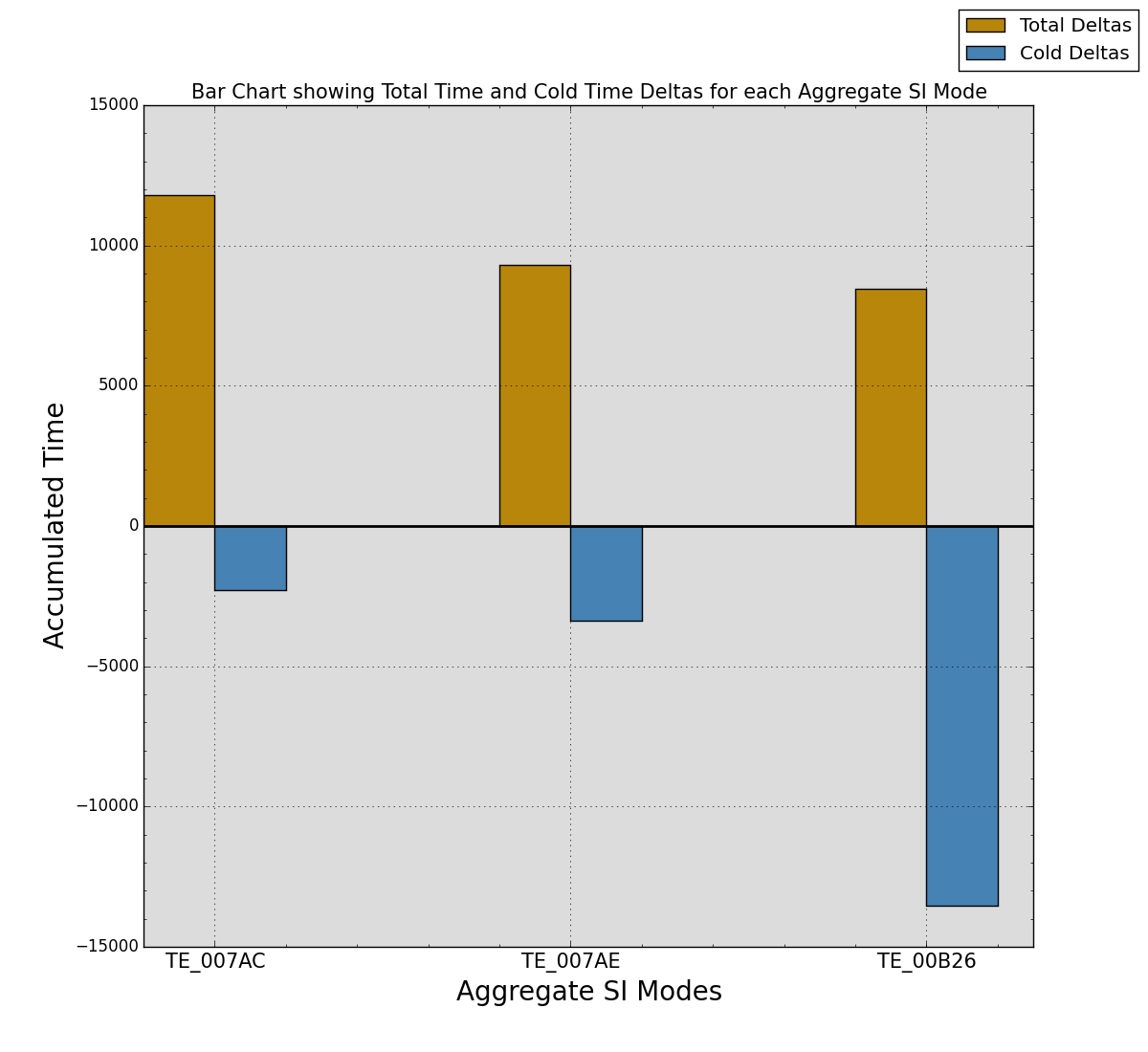

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Expected Time (secs) | 68400 | 38000 | 60800 |

| Total Actual Time (secs) | 80182 | 47313 | 69255 |

| Delta From Expected (secs) | 11782.00 | 9314.00 | 8455.00 |

| % of Expected Total (secs) | 117.23% | 124.51% | 113.91% |

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Exp. Cold Time (secs) | 41040.0 | 22800.0 | 36480.0 |

| Total Actual Cold Time (secs) | 38771 | 19417 | 22937 |

| Delta From Expected (secs) | -2268.86 | -3382.66 | -13542.29 |

| % of Exp. Cold Total (secs) | 94.47% | 85.16% | 62.88% |

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | |

|---|---|---|---|---|

| Primary 6 Chip SI Modes | TE_007AC | 9 | 80182.00 | 8909.11 |

| TE_007AE | 5 | 47314.00 | 9462.80 | |

| TE_00B26 | 7 | 60443.00 | 8634.71 | Old 6 Chip SI Modes | TE_00216 | 0 | 0.00 | 0.00 |

| TE_0021C | 0 | 0.00 | 0.00 | |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 1 | 8812.00 | 8812.00 |

| TE_00CA8 | 0 | 0.00 | 0.00 | 4 Chip SI Modes | TE_00C62 | 0 | 0.00 | 0.00 |

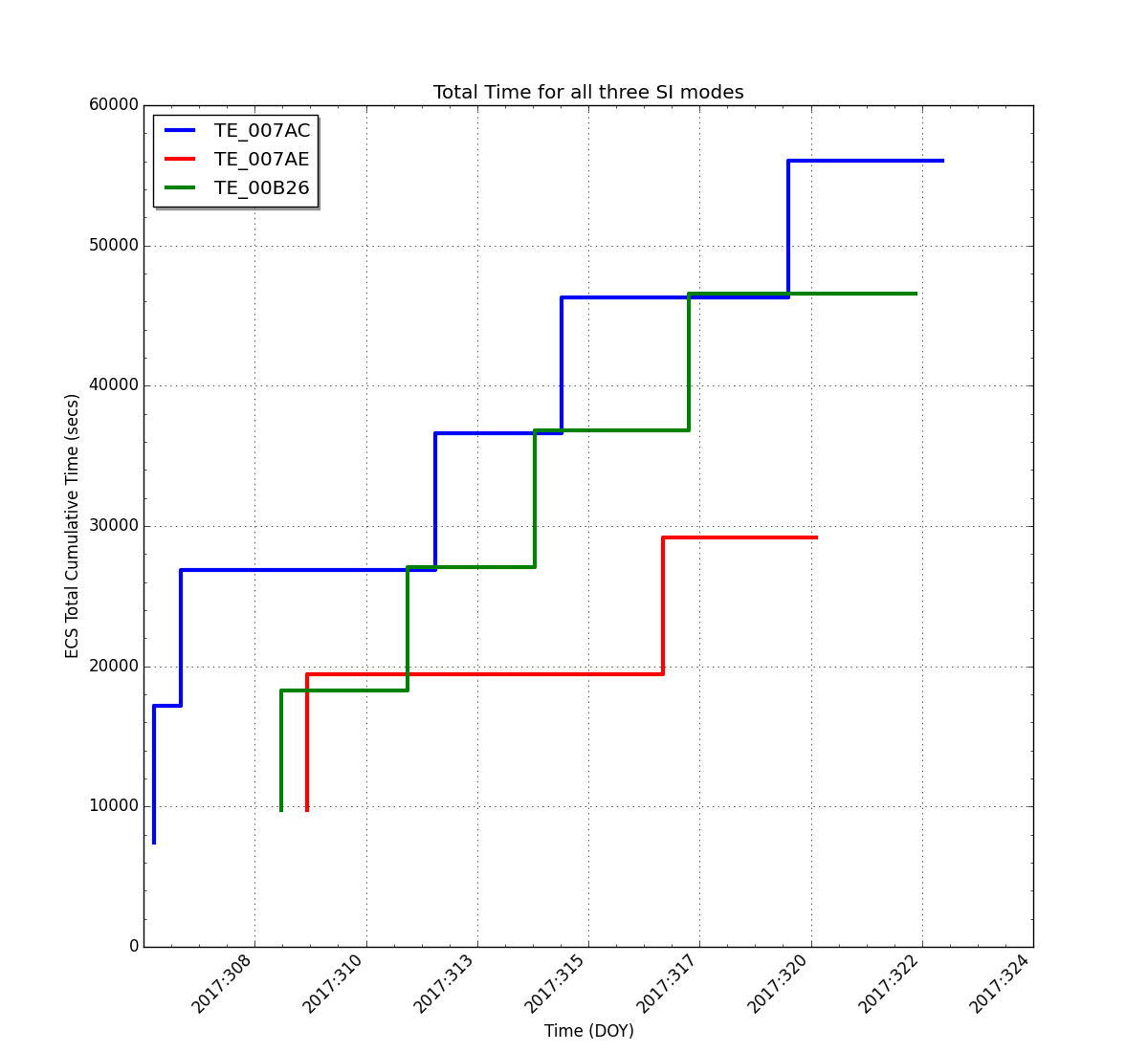

III. Statistics Since the Start of the Current Epoch

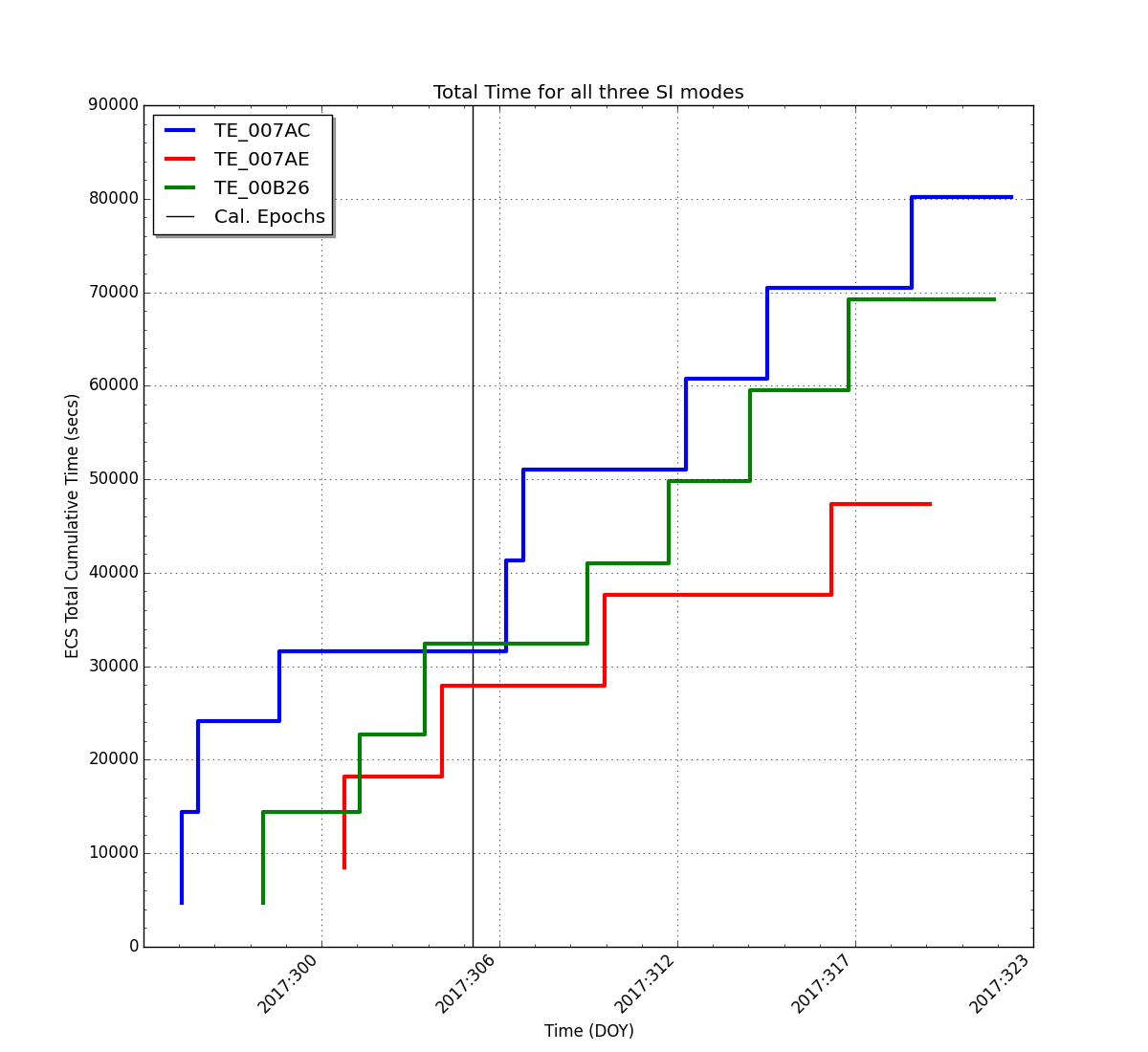

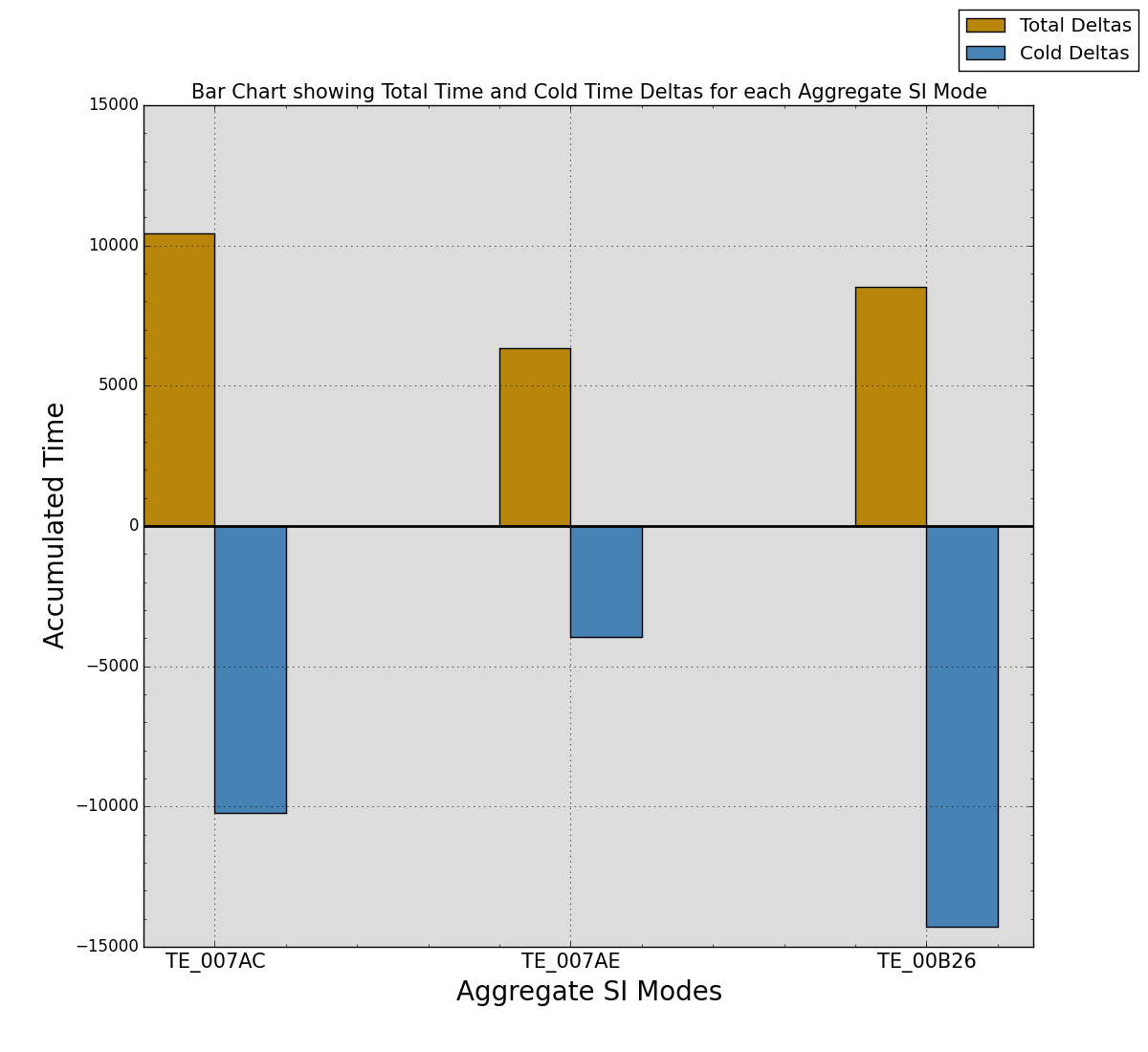

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Expected Time (secs) | 45600 | 22800 | 38000 |

| Total Actual Time (secs) | 56031 | 29151 | 46535 |

| Delta From Expected (secs) | 10431.00 | 6351.00 | 8535.00 |

| % of Expected Total (secs) | 122.88% | 127.86% | 122.46% |

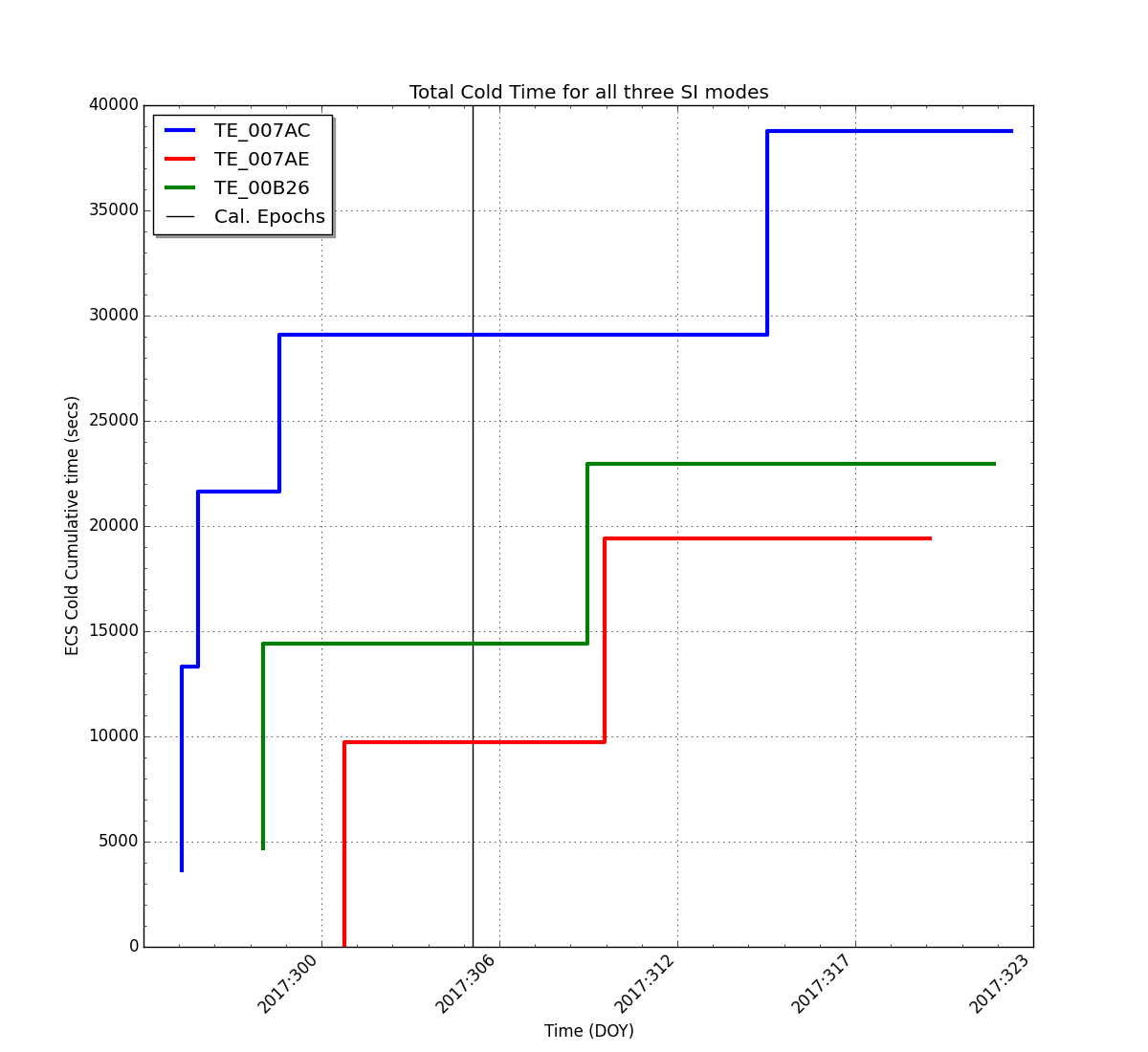

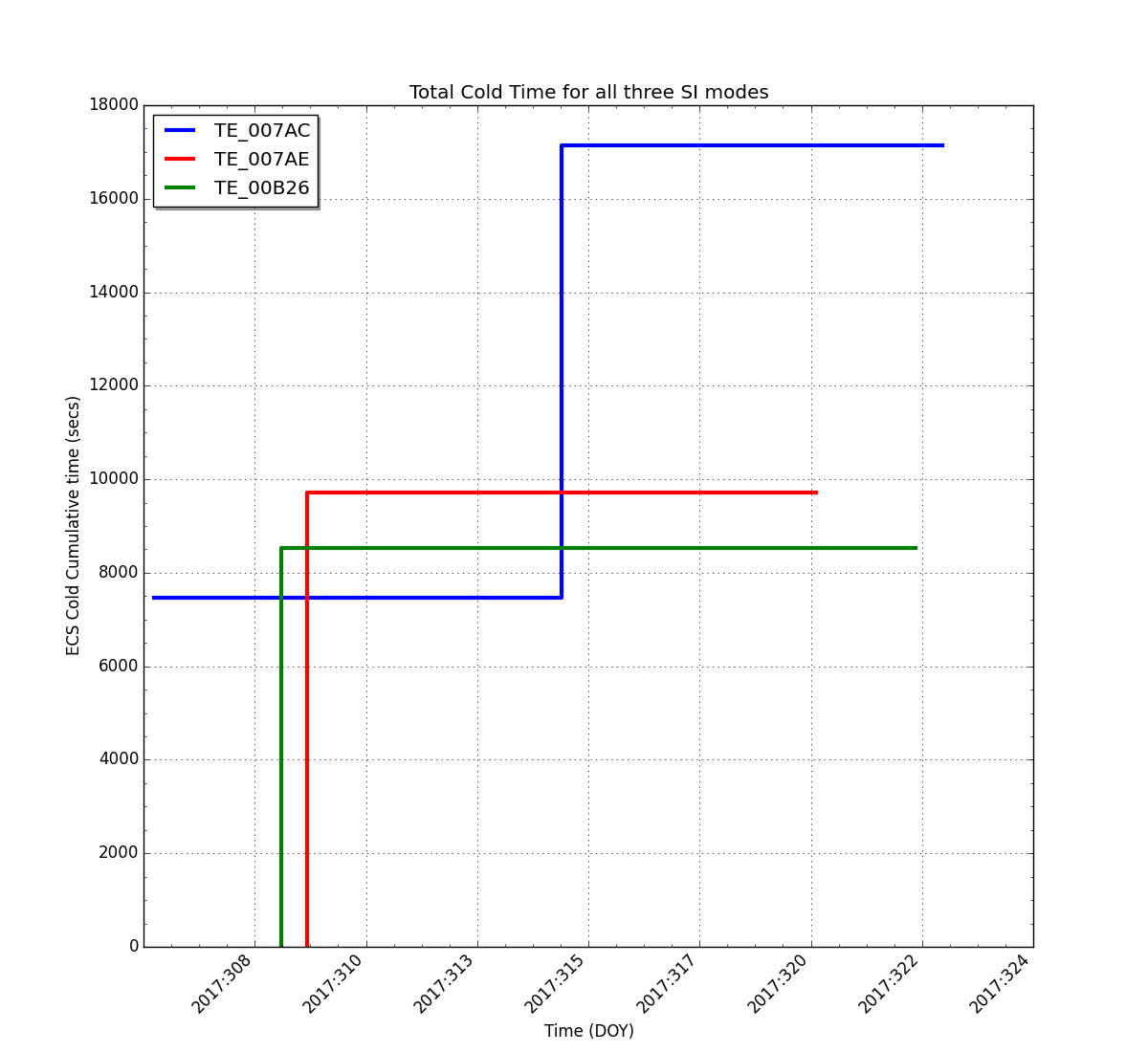

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Exp. Cold Time (secs) | 27360.0 | 13680.0 | 22800.0 |

| Total Actual Cold Time (secs) | 17143 | 9708 | 8525 |

| Delta From Expected (secs) | -10216.36 | -3971.46 | -14274.31 |

| % of Exp. Cold Total (secs) | 62.66% | 70.97% | 37.39% |

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | |

|---|---|---|---|---|

| Primary 6 Chip SI Modes | TE_007AC | 6 | 56031.00 | 9338.50 |

| TE_007AE | 3 | 29151.00 | 9717.00 | |

| TE_00B26 | 4 | 37723.00 | 9430.75 | Old 6 Chip SI Modes | TE_00216 | 0 | 0.00 | 0.00 |

| TE_0021C | 0 | 0.00 | 0.00 | |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 1 | 8812.00 | 8812.00 |

| TE_00CA8 | 0 | 0.00 | 0.00 | 4 Chip SI Modes | TE_00C62 | 0 | 0.00 | 0.00 |

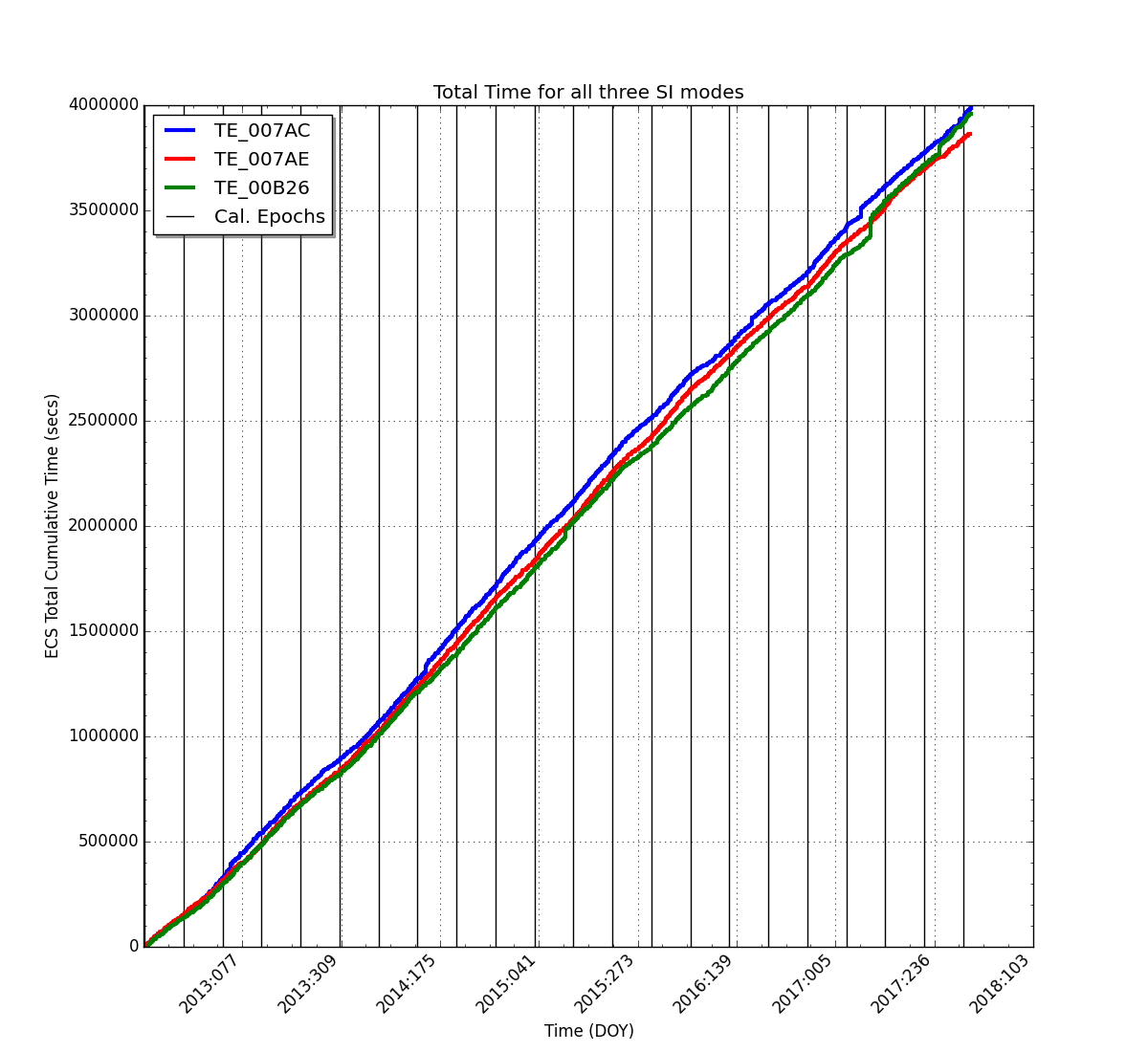

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Expected Time (secs) | 3640400 | 3587200 | 3579600 |

| Total Actual Time (secs) | 3985905 | 3865150 | 3961203 |

| Delta From Expected (secs) | 345505.52 | 277950.04 | 381603.65 |

| % of Expected Total (secs) | 109.49% | 107.75% | 110.66% |

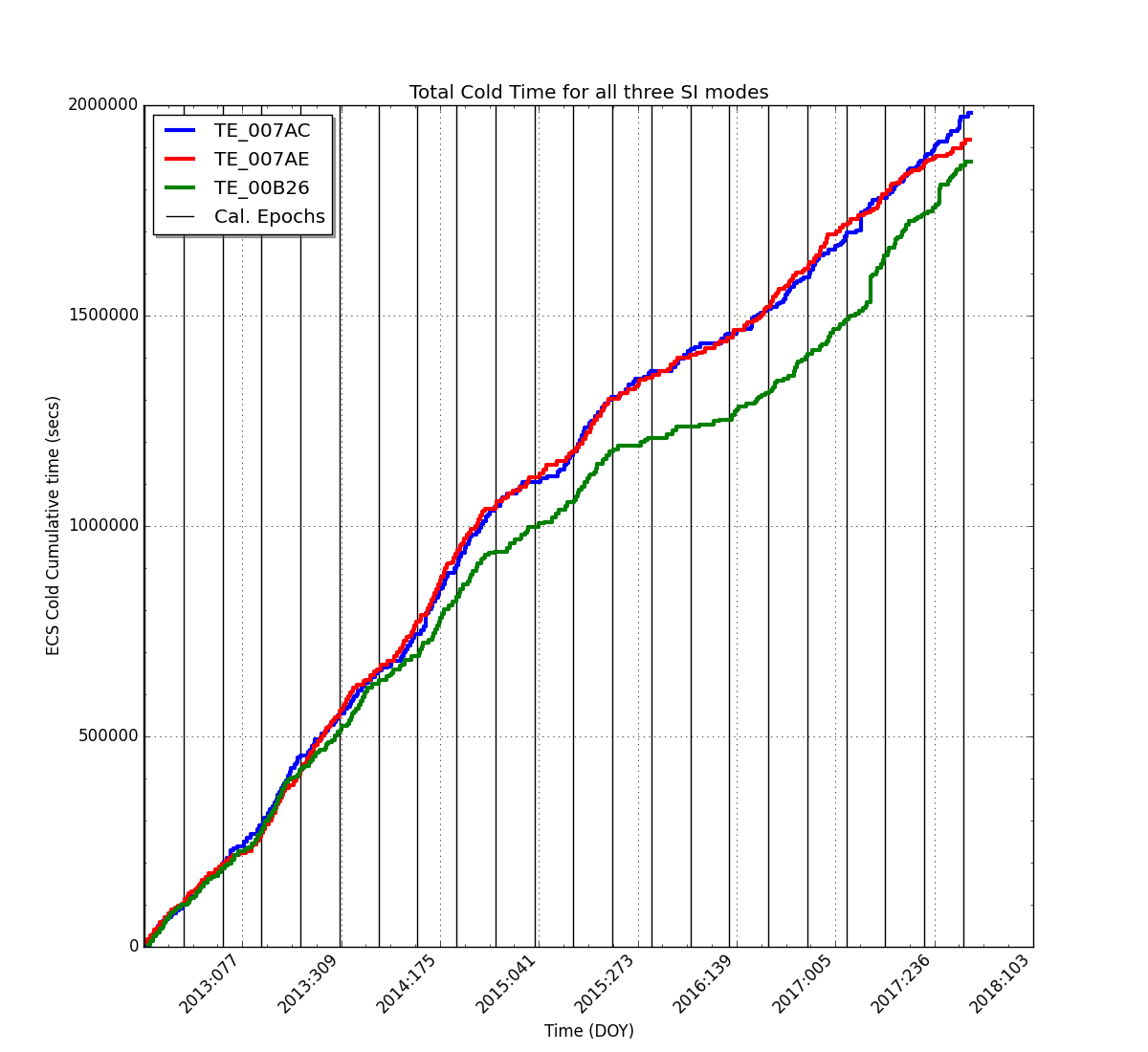

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Exp. Cold Time (secs) | 2184240.0 | 2152320.0 | 2147760.0 |

| Total Actual Cold Time (secs) | 1981554 | 1918066 | 1865720 |

| Delta From Expected (secs) | -202685.55 | -234253.02 | -282039.78 |

| % of Exp. Cold Total (secs) | 90.72% | 89.12% | 86.87% |

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | |

|---|---|---|---|---|

| Primary 6 Chip SI Modes | TE_007AC | 476 | 3926125.52 | 8248.16 |

| TE_007AE | 470 | 3849340.04 | 8190.09 | |

| TE_00B26 | 467 | 3820712.93 | 8181.40 | Old 6 Chip SI Modes | TE_00216 | 5 | 478338.25 | 95667.65 |

| TE_0021C | 0 | 0.00 | 0.00 | |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 4 | 32744.00 | 8186.00 |

| TE_00CA8 | 2 | 15810.00 | 7905.00 | 4 Chip SI Modes | TE_00C62 | 3 | 167526.73 | 55842.24 |

A word about the COLD Time stats:

- The Total Expected Cold Time value in the table below is 60.0% of the Total Expected Time (see Table above).

- Total Actual Cold Time is the sum of all time during each measurement where the temperature was <= -118.7 degrees C

- % of Expected Total is the fraction of the Total Expected Time achieved

SI Mode Mapping between 6,5 and 4 chip modes:

The 6 chip SI Modes consist of three distinct modes. But there are only 2, 5 chip SI Modes and only one 4 chip SI mode. To make tracking feasible, the 4 and 5 chip modes were mapped into the 6 chip modes in the following manner:

6 chip 5 chip 4 chip

TE_007AC -> TE_00C60 TE_00C62

TE_00B26 -> TE_00C60 TE_00C62

TE_007AE -> TE_00CA8

All of the TE_00CA8s get counted as TE_007AE

Half of the TE_00C60s get counted towards TE_007AC and the other half get counted with the TE_00B26s

Half of the TE_00C62s get counted towards TE_007AC and the other half get counted with the TE_00B26s.

So watchout for TE_00B26 over-representation.

Back To Top