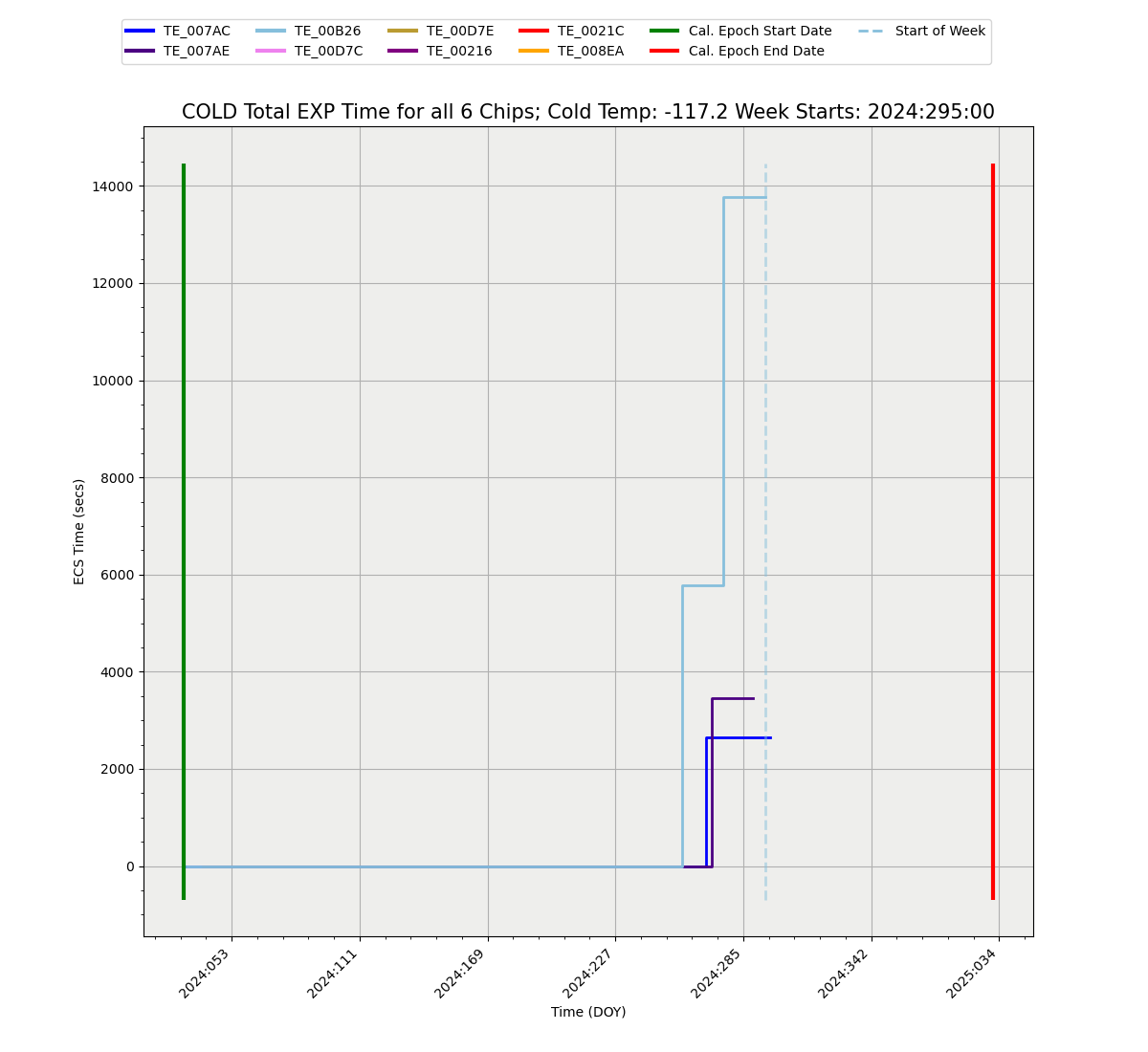

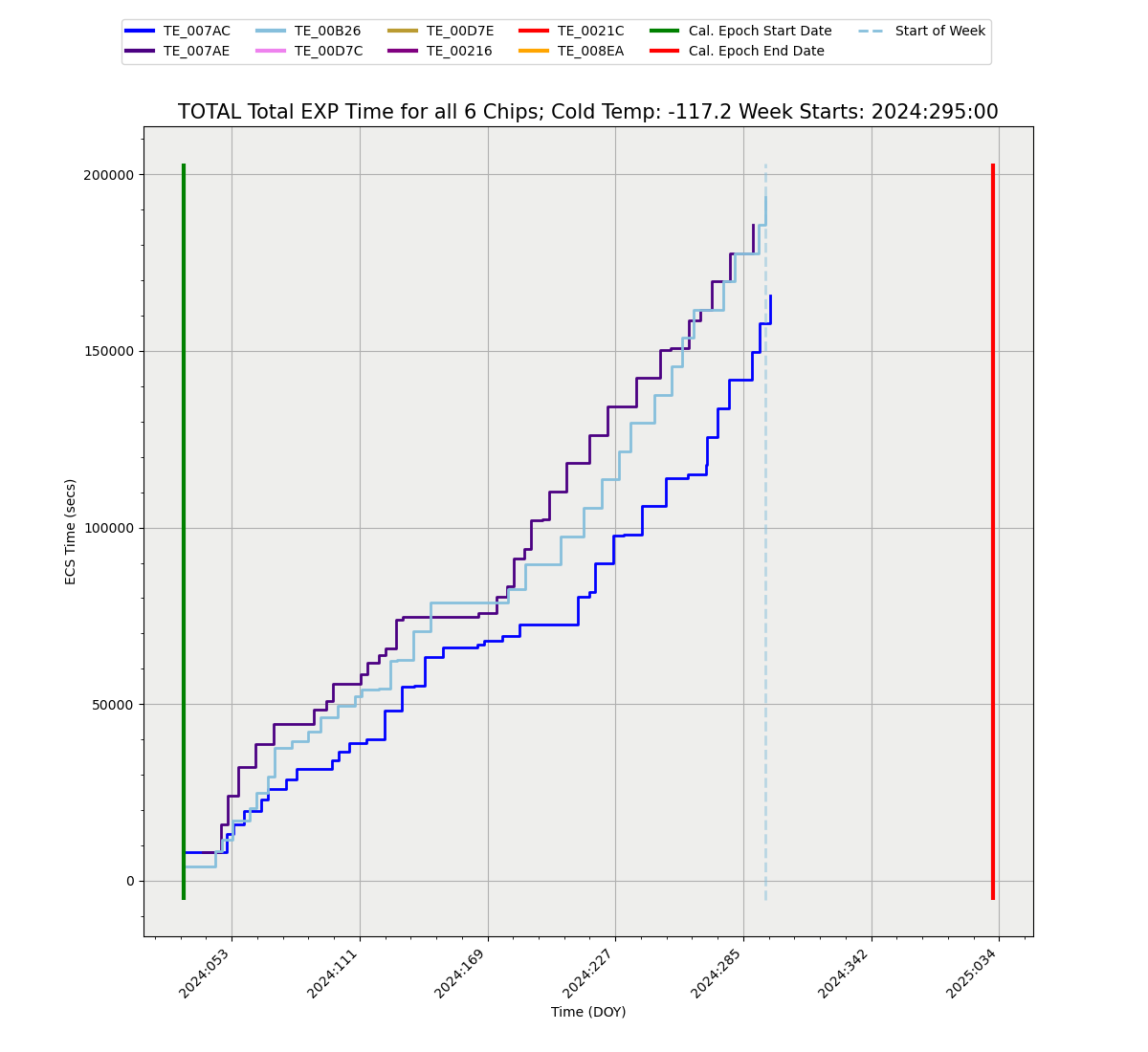

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | Primary 6 Chip SI Modes | TE_007AC | 40 | 165807.2 | 5837.7 |

|---|---|---|---|

| TE_007AE | 35 | 185705.20 | 7006.46 |

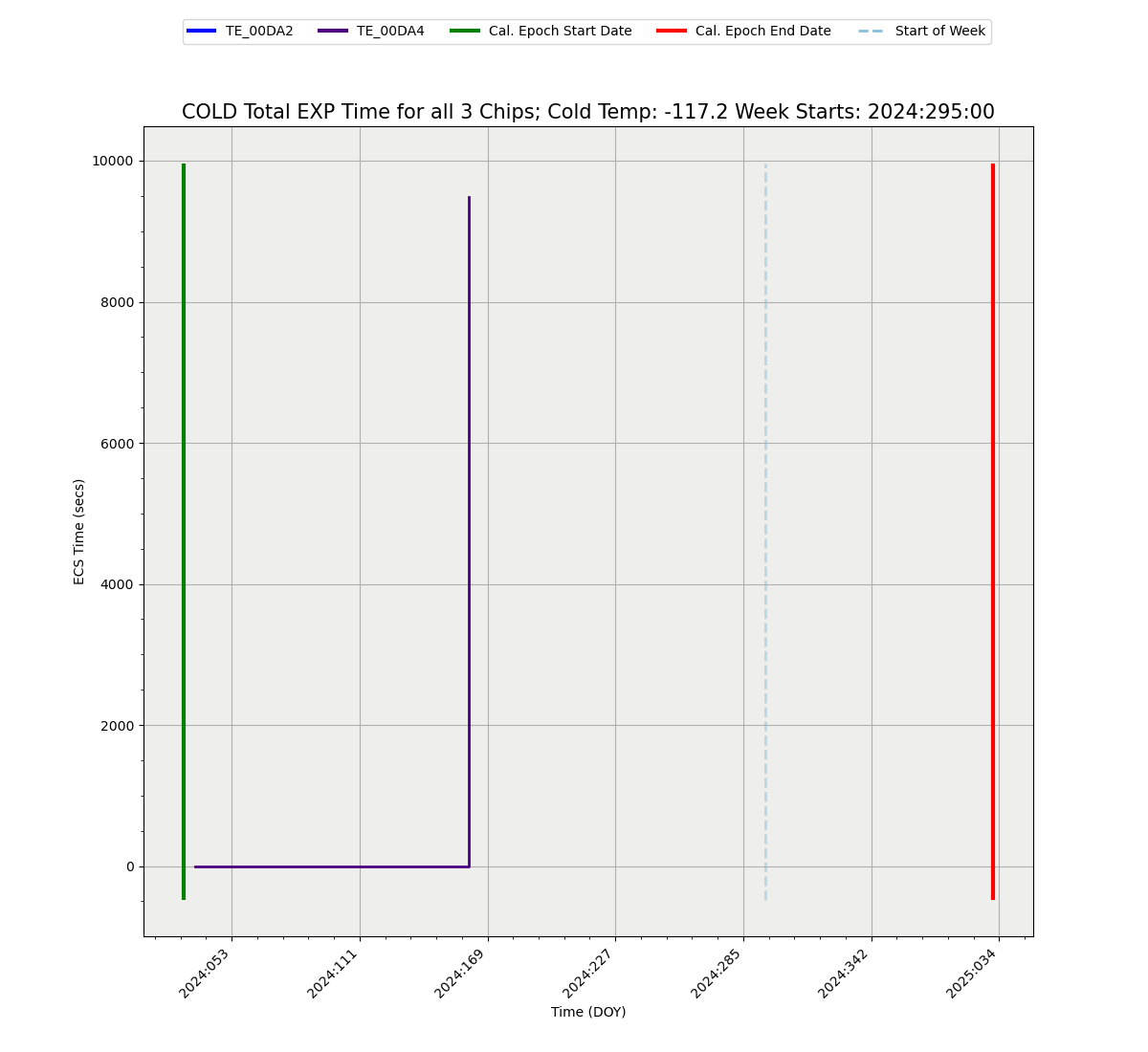

| TE_00B26 | 38 | 193723.53 | 6786.80 | Old 6 Chip SI Modes | TE_00216 | 0 | 0.00 | 0.00 |

| TE_0021C | 0 | 0.00 | 0.00 |

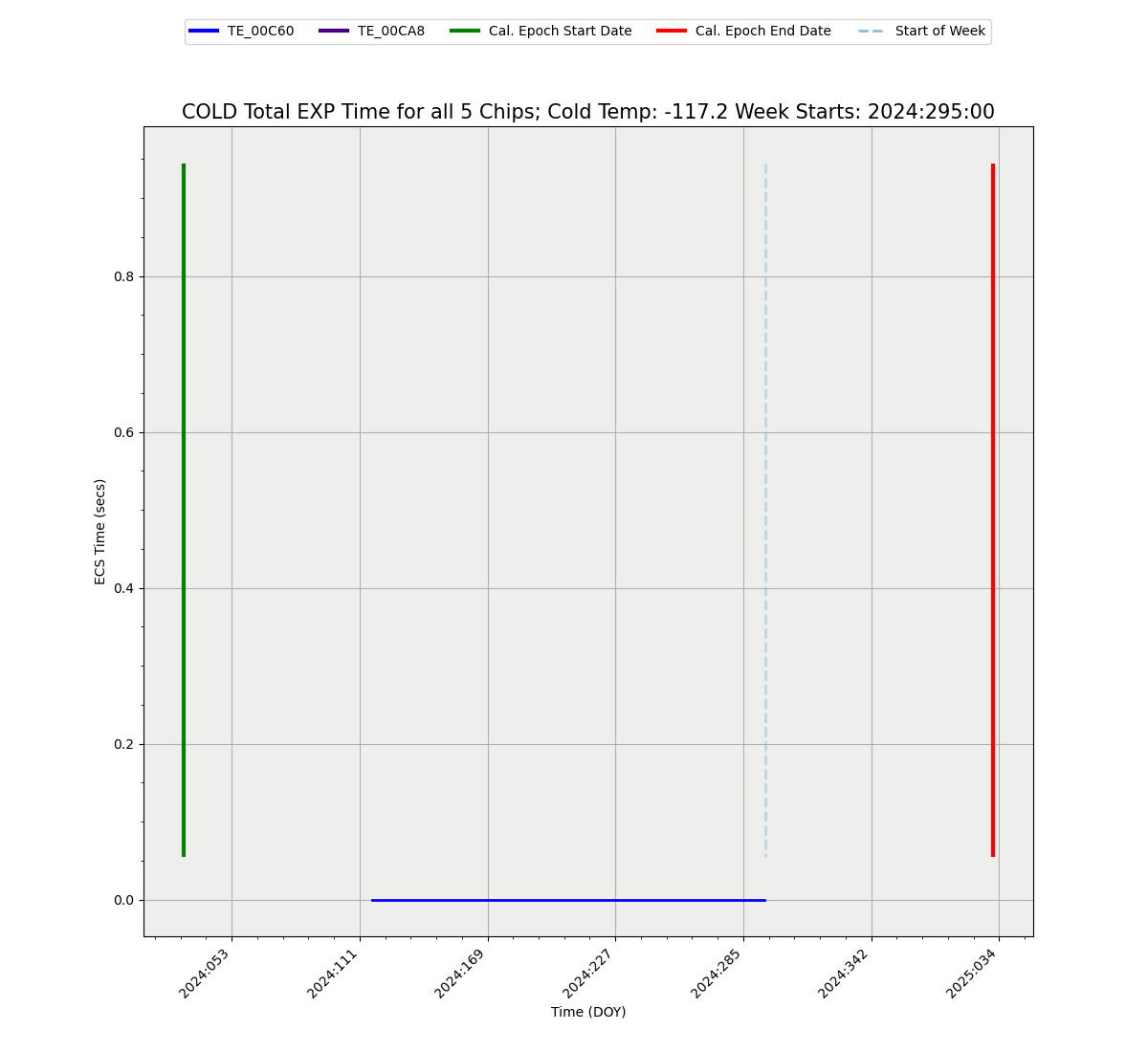

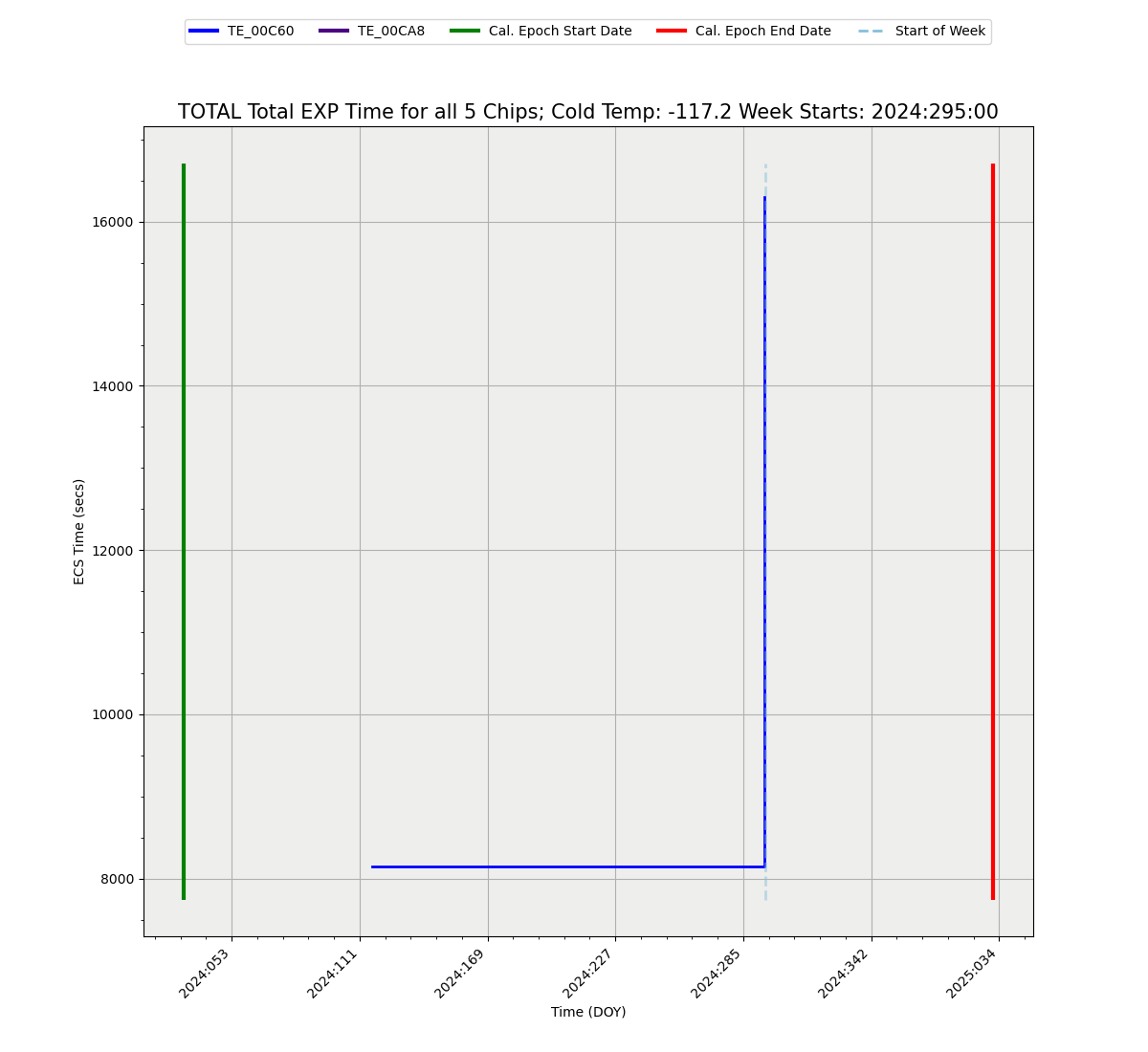

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 2 | 16305.20 | 9721.00 |

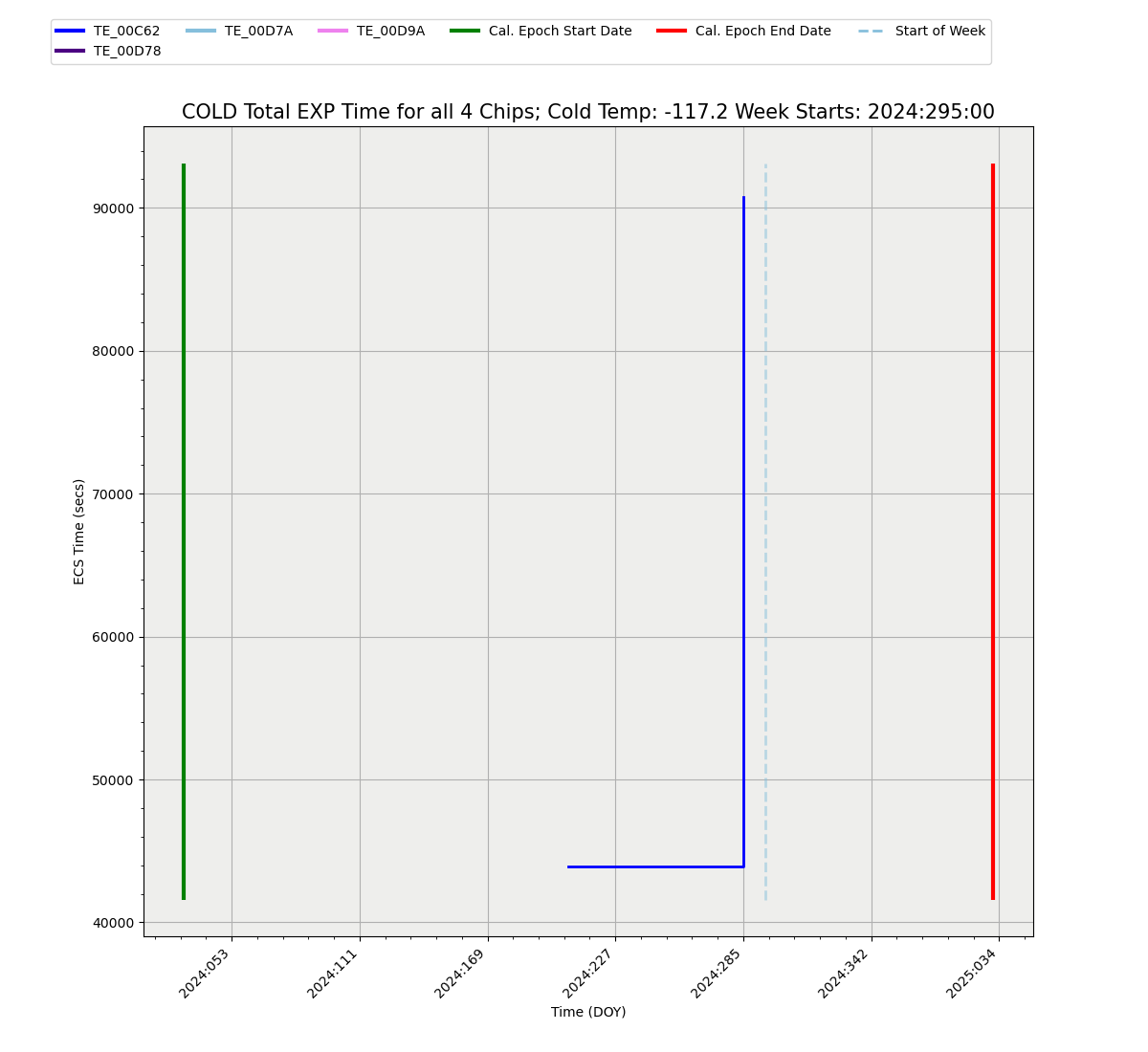

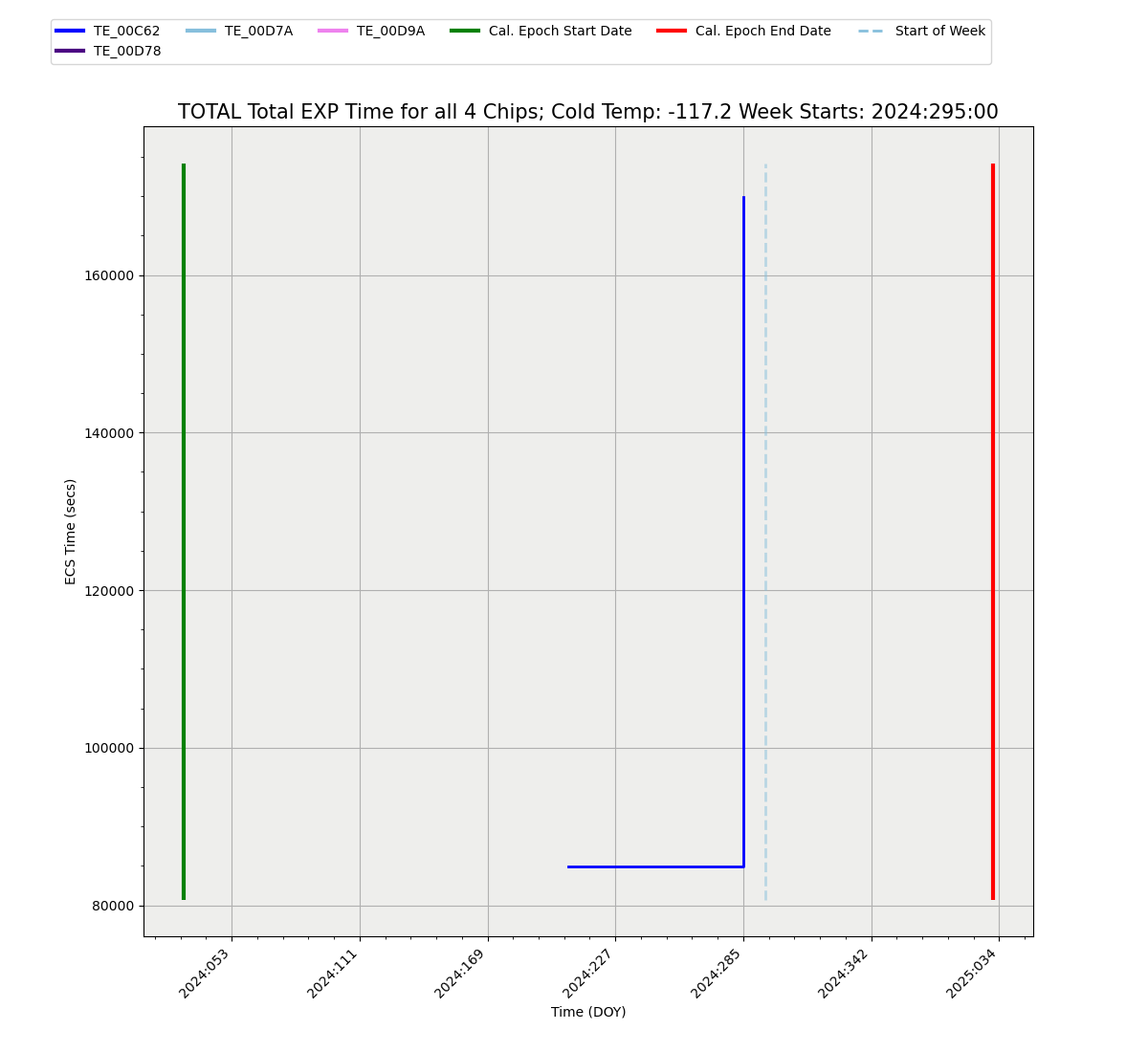

| TE_00CA8 | 0 | 0.00 | 0.00 | 4 Chip SI Modes | TE_00C62 | 2 | 169958.80 | 86408.00 | Totals: | 119 | 901739.6 |

Important Notes:

The Rules:

The rules to be followed are:Rule #1: The key time period for balancing SI mode statistics is the 6 month Epoch

By the end of the epoch, the SI mode statistics should match the rules stated below.

Rule #2: Each of the three, default, 6 chip, SI modes (or their 5 chip equivalents) must be used

at least once in each load week.

- If two SI modes are lagging in either cold time or total time, apportion the week's ECS

measurements between the two of them roughly commensurate with the amount they are lagging.

- The 6 month Epoch allows "even" correction of two lagging SI modes. No

need to pile a weeks worth of ECS measurements on one SI mode if two are lagging.

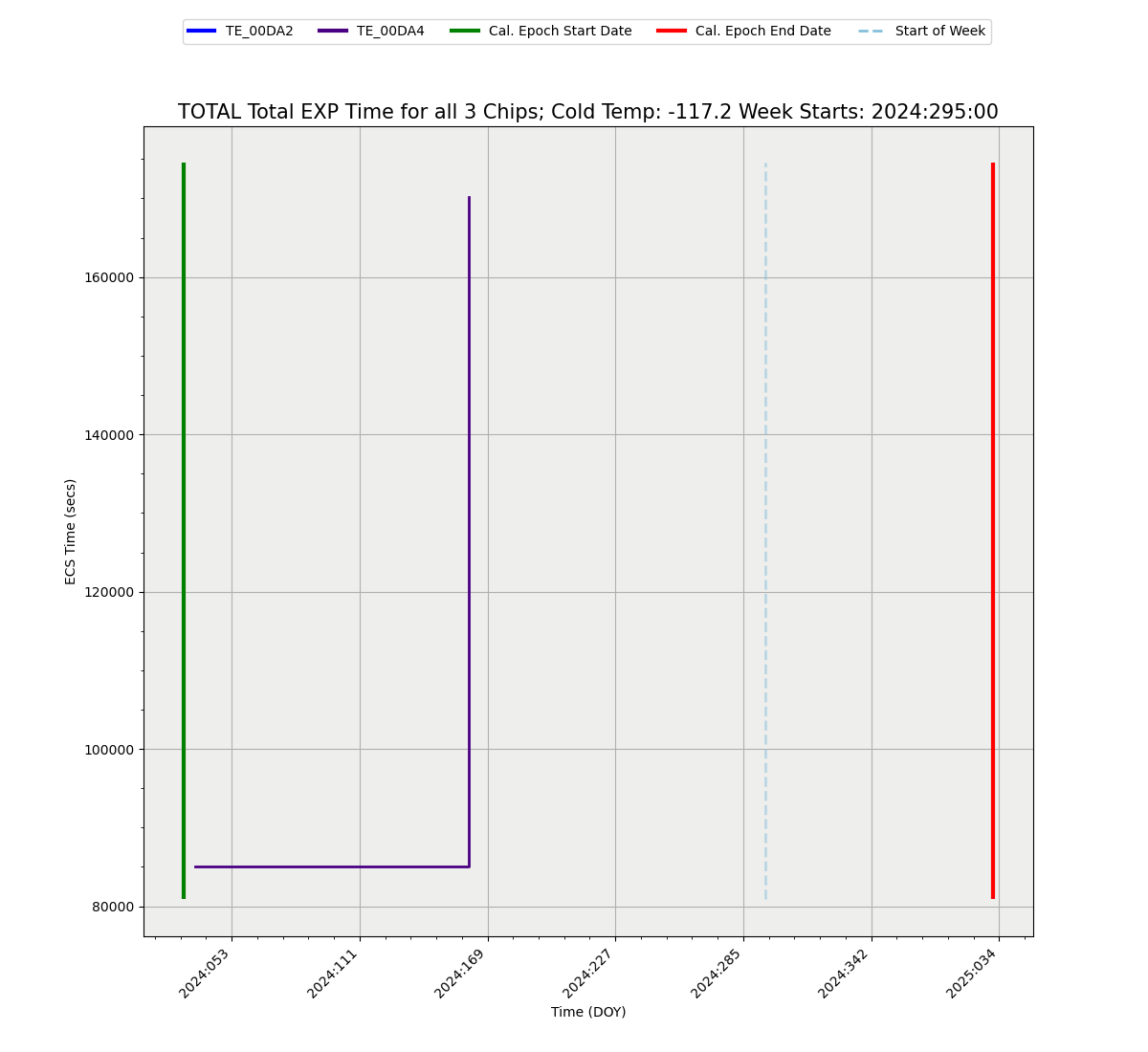

Rule #3: Make certain to spread the amount of COLD ECS time as evenly as possible across all three SI modes

Balance Cold measurement data between the three default 6-chip modes within 10%

of each other on an Epoch basis

Rule #4: Spread the amount of *Total* ECS time as evenly as possible across all three SI modes.

- Balance Total measurement data between the three default 6-chip modes within 10%

of each other on an Epoch basis.

Rule #3 takes precedence over Rule #4.

Rule #5: At least 60% of scheduled ECS measurement time must be -119.2 deg. C

Rule #6: Any ECS measurements during a Perigee Passage that are cold MUST be assigned to the nominal

ECS SI modes. i.e. Any requested Rawmode runs can be done with a warm focal plane.

Back To Top

Presently, the only 6 chip SI modes used during Perigee Passages are:

A word about the COLD Time stats:

Cold Time is defiined by focal plane temperatures <= -117.2 degrees C.

Guidance for SI Mode Mapping between 6, 5 and 4 chip modes:

The 6 chip SI Mode set consist of five modes. But there are only two, 5 chip SI Modes and only three, 4 chip SI modes. So there is not a one to one mapping of 6 to 5 to 4 chips with unique modes. Here is the chip-drop rule set as presently defined:

6 chip 5 chip 4 chip

TE_007AC -> TE_00C60 -> TE_00D78

TE_00B26 -> TE_00C60 -> TE_00D78

TE_007AE -> TE_00CA8 -> TE_00D78

TE_00D7C -> TBD

TE_00D7E -> TBD

1) TE_007AC

2) TE_00B26

3) TE_007AESI Mode to Chip Mappings:

6 Chip SI Modes

TE_007AC - I0-I3 + S2-S3

TE_00B26 - I0-I3 + S1,S3

TE_007AE - S0-S5

TE_00D7C - I0-I1 + S1-S4

TE_00D7E - I2-I3 + S1-S4

5 Chip SI Modes

TE_00C60 - I0-I3 + S3

TE_00CA8 - S1-S5

4 Chip SI Modes

TE_00C62 - I1-I3 + S3

TE_00D78 - I0-I3

TE_00D7A - S1-S4

Back To Top